## Introduction to Embedded Systems

#### **Branden Ghena**

UC Berkeley EECS 149/249A Fall 2019

Content by Prabal Dutta, Edward Lee, and others © 2008-2017: E. A. Lee, A. L. Sangiovanni-Vincentelli, S. A. Seshia. All rights reserved.

**Chapter 9: Memory Architectures**

- Education: 7th year PhD student

Im

Im

- Indergrad: Michigan Tech

- Master's: University of Michigan

#### **•** Teaching:

- 3 Summer 2019: CS61C

- 3 Fall 2018: EE149/CS249A

- On the job market for lecturer positions this fall!

- Research: Low-power wireless communications

### **Introducing Branden**

### Today's Topic: Memory Architectures

#### **Computer Memory**

- Physical Types

- SRAM, Flash, Disks

- Hardware Architectures

- Registers, Caches, Primary Memory

- Software

- Stack, Heap, Code

#### Mostly Review (for some of you)

- With embedded systems twists

- For more details on normal non-embedded computers see CS61C

- <u>https://inst.eecs.berkeley.edu/~cs61c/su19/#lectures</u>

- Particularly "C Memory Management" and "Caches"

### Outline

#### o Memory Overview

- Types of Memory

- Memory Hierarchy

#### o Embedded Systems Memory

- Memory Maps

- Memory-Mapped I/O

- Lab Hardware Examples

#### o Memory Organization

- Stacks & Heaps

- Code examples

# **TYPES OF MEMORY**

**Memory Classes**

Two major types

## 1. Memory which is temporary Volatile Memory

2. Memory which is permanent Non-Volatile Memory

### Volatile Memory Loses contents when power is off.

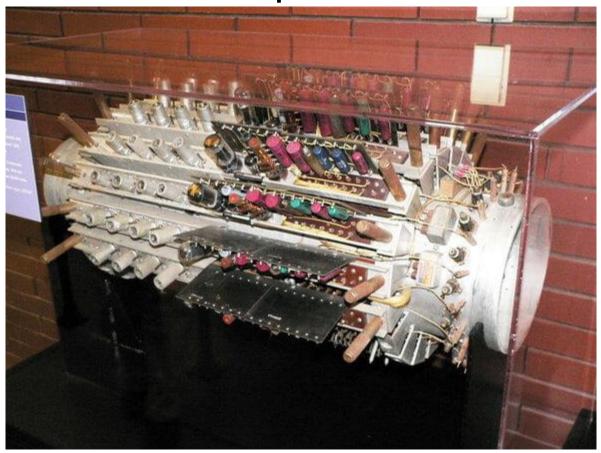

• How much memory do you think this stores?

### Volatile Memory Loses contents when power is off.

- Mercury Delay Line (UNIVAC)

- Roughly 2000 bytes for the entire tank

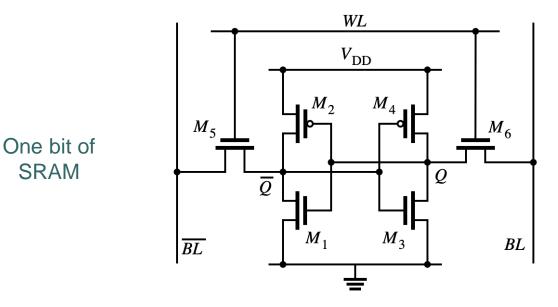

#### Volatile Memory Loses contents when power is off.

- SRAM: static random-access memory

- Fast, deterministic access time

- Used for registers, caches, and small embedded memories

- But more power hungry and less dense than DRAM

### Volatile Memory

Loses contents when power is off.

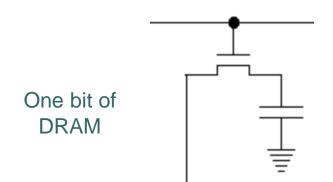

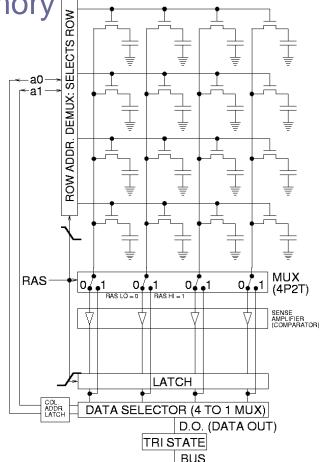

- DRAM: dynamic random-access memory

- Slower than SRAM

- Access time depends on the sequence of addresses

- Denser than SRAM (higher capacity)

- Requires periodic refresh (typically every 64 milliseconds)

- Typically used for main memory

### Non-Volatile Memory

Preserves contents when power is off

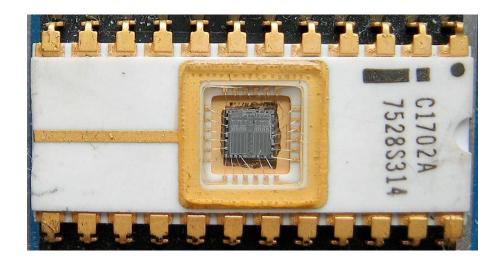

- EPROM: erasable programmable read only memory

- Invented by Dov Frohman of Intel in 1971

- Erase by exposing the chip to strong UV light

- EEPROM: electrically erasable programmable read-only memory

- Invented by George Perlegos at Intel in 1978

Image from the Wikimedia Commons

## Non-Volatile Memory

Preserves contents when power is off

- Disk drives

- Not as well suited for embedded systems

- Flash memory

- Invented by Dr. Fujio Masuoka at Toshiba around 1980

- Erased a "block" at a time

- Limited number of program/erase cycles (~100,000)

- Controllers can get quite complex

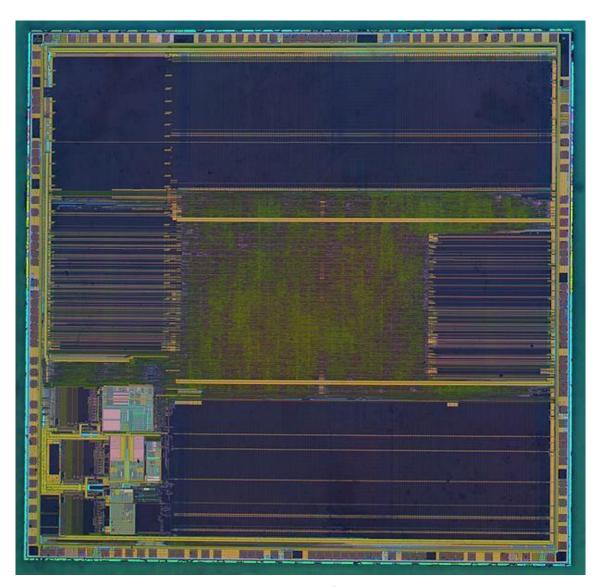

### Example:

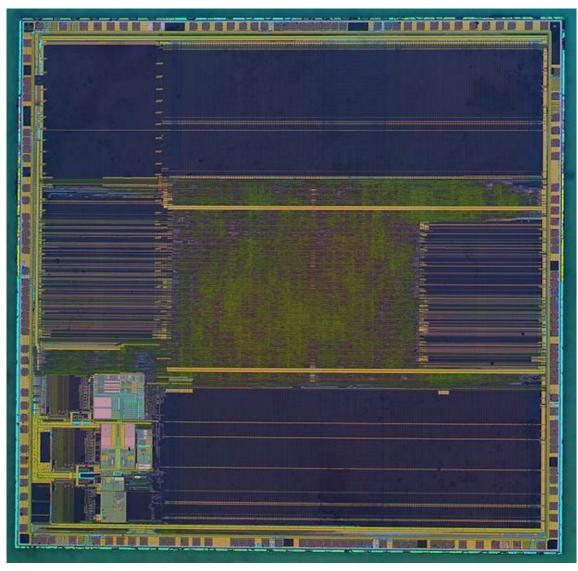

Die of a STM32F103VGT6 ARM Cortex-M3 microcontroller with 1 megabyte flash memory by STMicroelectronics.

Which part is the memory?

Image from Wikimedia Commons

#### Example:

Die of a STM32F103VGT6 ARM Cortex-M3 microcontroller with 1 megabyte flash memory by STMicroelectronics.

# Which part is the memory?

Just about everything but the bottom right corner

Image from Wikimedia Commons

# **MEMORY HIERARCHIES**

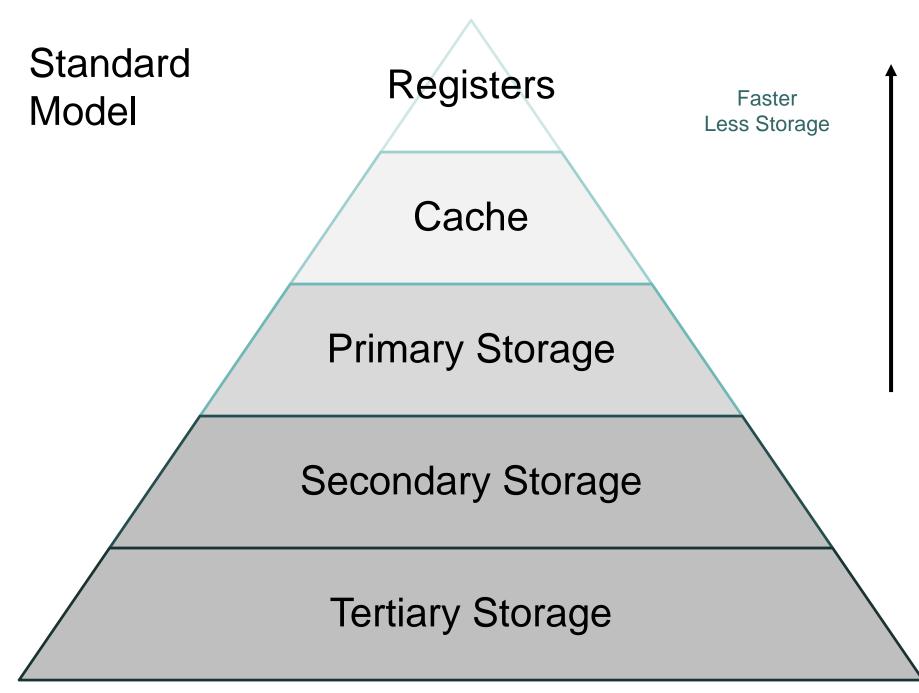

#### Memory Hierarchy

- Memories on a system can be arranged as a pyramid

- Top is the most frequently used memory

- Bottom is the least frequently used

- o Let's draw the hierarchy pyramid

- What are the capabilities and constraints as you move up and down the hierarchy? Which are volatile/non-volatile?

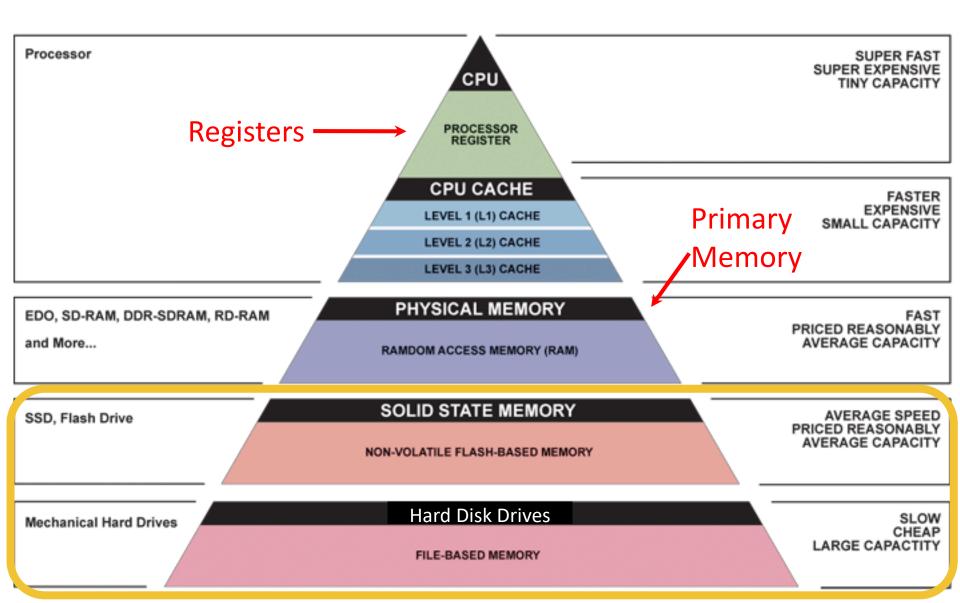

#### Personal Computer Memory Hierarchy

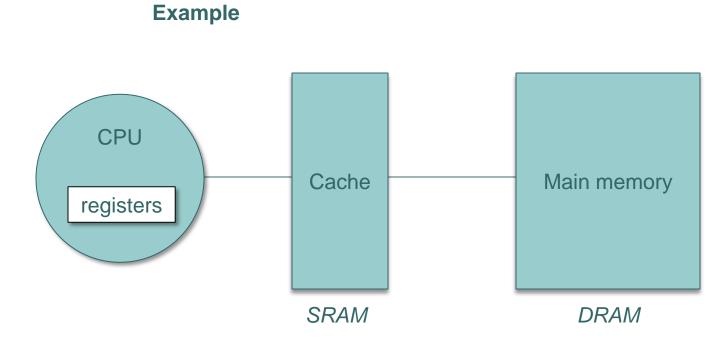

### **Accessing Memories**

How do you access:

- Registers

- Directly in assembly code

- Cache

- Automatically handled by hardware

- RAM

- Load/Store instructions in assembly code

- This is the main memory for the system

- Disk

- The OS handles copying pages into RAM

### Outline

#### o Memory Overview

- Types of Memory

- Memory Hierarchy

#### o Embedded Systems Memory

- Memory Maps

- Memory-Mapped I/O

- Lab Hardware Examples

#### o Memory Organization

- Stacks & Heaps

- Code examples

# MEMORY MAPS

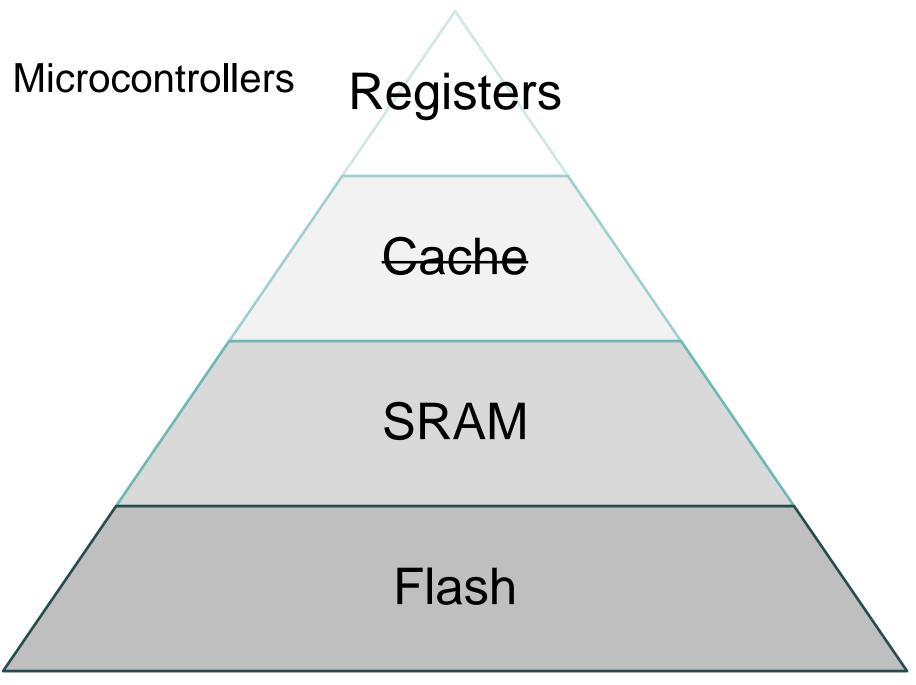

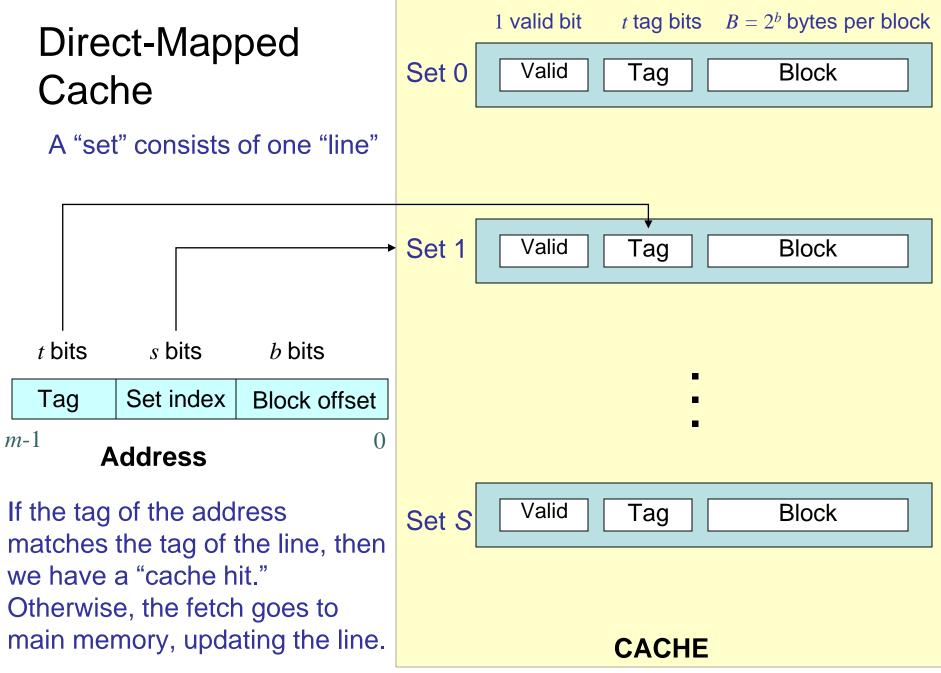

#### Caches in Embedded Systems

Why do embedded systems avoid using caches?

#### Caches in Embedded Systems

Why do embedded systems avoid using caches?

Caches improve performance, but making timing unreliable (could be faster or slower in any given case) A Fact About the 20<sup>th</sup> Century Notion of Computing: Timing is not Part of Software Semantics

**Correct** execution of a program in C, C#, Java, Haskell, OCaml, Esterel, etc. has nothing to do with how long it takes to do anything. Nearly all our computation and networking abstractions are built on this premise.

Caches improve *performance* for a fixed cost, at the expense of making it very difficult to control timing.

149/249A, UC Berkelev

### **Accessing Embedded Memories**

How do you access:

- Registers

- Directly in assembly code

- SRAM (Volatile)

- Load/Store instructions in assembly code

- Variables are stored in here

- Flash (Non-Volatile)

- Load instructions in assembly code (Read-Only)

- Code executes from here

Note: no virtual memory!!

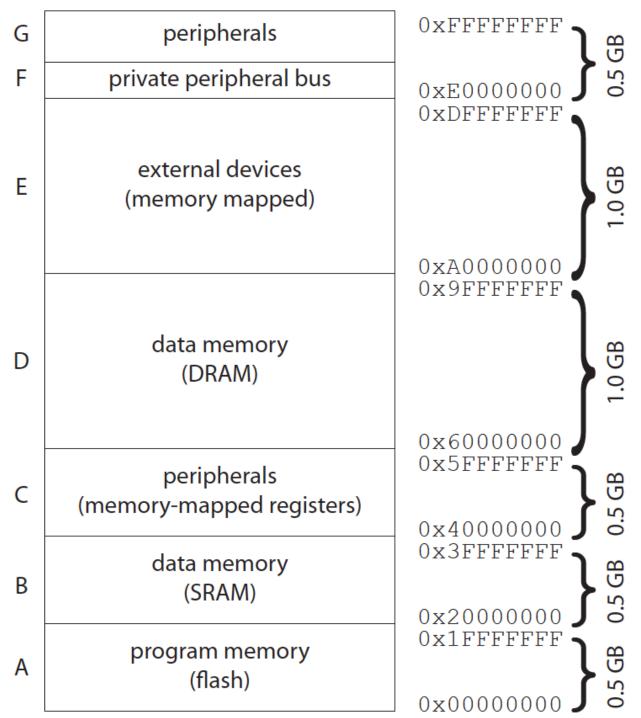

Memory Map of an ARM Cortex - M3 architecture Defines the mapping of addresses to physical memory. Why do this? Note that this does not define how much physical memory there is!

### Main Memory on Personal Computers

- Applications on personal computers don't see a memory map like the Cortex-M3 one

- Why not?

- What does their memory look like?

#### Main Memory on Personal Computers

- Applications on personal computers don't see a memory map like the Cortex-M3 one

- Why not?

- What does their memory look like?

Applications are provided virtual memory spaces, where it appears as if they own all addresses and start at address 0. This makes them easier to create and more secure.

How this is implemented quickly and securely are major topics of Operating Systems and Computer Architecture

# MEMORY-MAPPED I/O

### Things That Aren't Memory

#### • Microcontrollers have a lot of peripherals

- General Purpose I/O (GPIO) pins

- Analog to Digital Converters

- Digital to Analog Converters

- Pulse-Width Modulation Generators

- Timers

- Various communication buses: UART, SPI, I<sup>2</sup>C

- How do they access the peripherals?

- Why not create special assembly functions to access them?

### Things That Aren't Memory

#### • Microcontrollers have a lot of peripherals

- General Purpose I/O (GPIO) pins

- Analog to Digital Converters

- Digital to Analog Converters

- Pulse-Width Modulation Generators

- Timers

- Various communication buses: UART, SPI, I<sup>2</sup>C

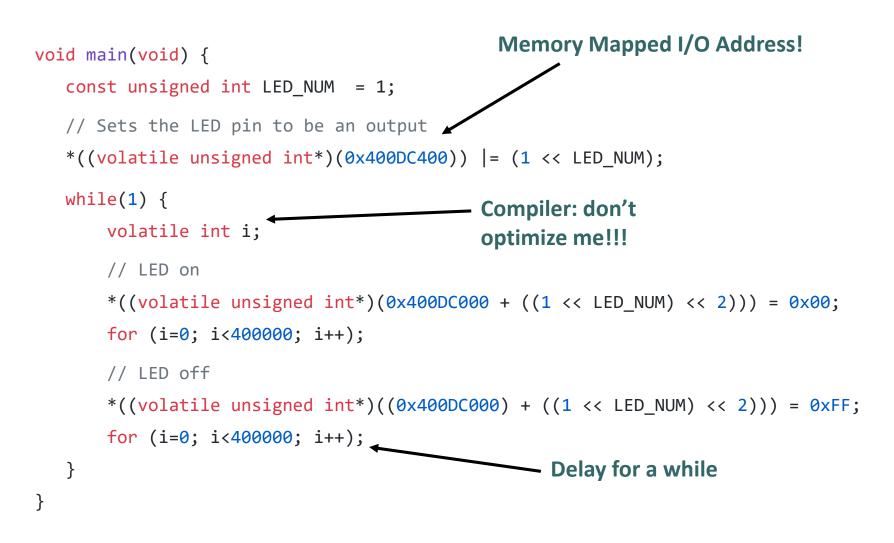

- How do they access the peripherals? With memory reads and writes

- Why not create special assembly functions to access them?

That would make the processor harder to design. In the memorymapped case, one processor can use an arbitrary selection of peripherals and doesn't have to know anything about them.

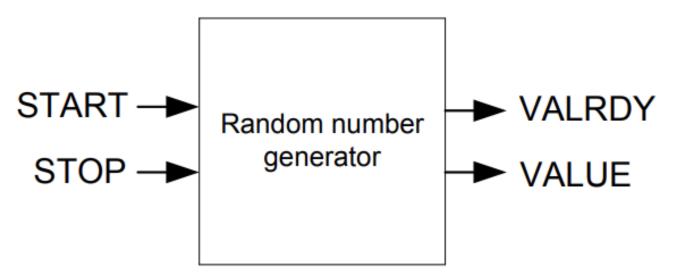

Example RNG peripheral from the nRF52832

Interface:

#### 26.3 Registers

#### **Table 45: Instances**

| Base address | Peripheral | Instance | Description             | Configuration |

|--------------|------------|----------|-------------------------|---------------|

| 0x4000D000   | RNG        | RNG      | Random Number Generator |               |

#### Table 46: Register Overview

| Register      | Offset | Description                                                                     |

|---------------|--------|---------------------------------------------------------------------------------|

| TASKS_START   | 0x000  | Task starting the random number generator                                       |

| TASKS_STOP    | 0x004  | Task stopping the random number generator                                       |

| EVENTS_VALRDY | 0x100  | Event being generated for every new random number written to the VALUE register |

| SHORTS        | 0x200  | Shortcut register                                                               |

| INTENSET      | 0x304  | Enable interrupt                                                                |

| INTENCLR      | 0x308  | Disable interrupt                                                               |

| CONFIG        | 0x504  | Configuration register                                                          |

| VALUE         | 0x508  | Output random number                                                            |

#### 26.3 Registers

# How do we access these registers from C code?

#### **Table 45: Instances**

| Base address | Peripheral | Instance | Description             | Configuration |

|--------------|------------|----------|-------------------------|---------------|

| 0x4000D000   | RNG        | RNG      | Random Number Generator |               |

#### **Table 46: Register Overview**

| Register      | Offset | Description                                                                     |

|---------------|--------|---------------------------------------------------------------------------------|

| TASKS_START   | 0x000  | Task starting the random number generator                                       |

| TASKS_STOP    | 0x004  | Task stopping the random number generator                                       |

| EVENTS_VALRDY | 0x100  | Event being generated for every new random number written to the VALUE register |

| SHORTS        | 0x200  | Shortcut register                                                               |

| INTENSET      | 0x304  | Enable interrupt                                                                |

| INTENCLR      | 0x308  | Disable interrupt                                                               |

| CONFIG        | 0x504  | Configuration register                                                          |

| VALUE         | 0x508  | Output random number                                                            |

#### 26.3 Registers

#### **Table 45: Instances**

| Base address | Peripheral | Instance |

|--------------|------------|----------|

| 0x4000D000   | RNG        | RNG      |

#### Table 46: Register Overview

# How do we access these registers from C code?

By reading and writing the raw address. (Although we usually create structures at that address to make things more clear)

| Register      | Offset | Description                                                                     |

|---------------|--------|---------------------------------------------------------------------------------|

| TASKS_START   | 0x000  | Task starting the random number generator                                       |

| TASKS_STOP    | 0x004  | Task stopping the random number generator                                       |

| EVENTS_VALRDY | 0x100  | Event being generated for every new random number written to the VALUE register |

| SHORTS        | 0x200  | Shortcut register                                                               |

| INTENSET      | 0x304  | Enable interrupt                                                                |

| INTENCLR      | 0x308  | Disable interrupt                                                               |

| CONFIG        | 0x504  | Configuration register                                                          |

| VALUE         | 0x508  | Output random number                                                            |

### 26.3 Registers

#### Table 45: Instances

| Base address | Peripheral |

|--------------|------------|

| 0x4000D000   | RNG        |

#### **Table 46: Register Overview**

| Offset |                                                             |

|--------|-------------------------------------------------------------|

| 0x000  |                                                             |

| 0x004  |                                                             |

| 0x100  |                                                             |

| 0x200  |                                                             |

| 0x304  |                                                             |

| 0x308  |                                                             |

| 0x504  |                                                             |

| 0x508  |                                                             |

|        | 0x000<br>0x004<br>0x100<br>0x200<br>0x304<br>0x308<br>0x504 |

#### #define NRF\_RNG\_BASE 0x4000D000

\*\*

\* @brief Random Number Generator (RNG) \*/

#### typedef struct {

- \_\_0 uint32\_t TASKS\_START;

- \_\_0 uint32\_t TASKS\_STOP;

- \_\_I uint32\_t RESERVED0[62];

- \_\_IO uint32\_t EVENTS\_VALRDY;

- \_\_I uint32\_t RESERVED1[63];

- \_\_\_IO uint32\_t SHORTS;

- \_\_I uint32\_t RESERVED2[64];

- \_\_IO uint32\_t INTENSET;

- \_\_IO uint32\_t INTENCLR;

- \_\_I uint32\_t RESERVED3[126];

- \_\_IO uint32\_t CONFIG;

- \_\_I uint32\_t VALUE;

- NRF\_RNG\_Type;

#define NRF\_RNG (NRF\_RNG\_Type\*)NRF\_RNG\_BASE;

### 26.3.5 VALUE

Address offset: 0x508

Output random number

| 31                | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20   | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|----|----|----|----|----|----|----|----|-----|-----|------|-----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                   |    |    |    |    |    |    |    |    |     |     |      |     |    |    |    |    |    |    |    |    |    |   |   | А | А | А | А | А | А | А | А |

| 0                 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Value Description |    |    |    |    |    |    |    |    |     |     |      |     |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| [0255]            |    |    |    |    |    |    |    |    | ner | ate | d ra | and | om | nu | mb | er |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

uint8\_t nrf\_rng\_random\_value\_get(void) {

return (uint8\_t)(NRF\_RNG->VALUE & RNG\_VALUE\_VALUE\_Msk);

### 26.3.5 VALUE

Address offset: 0x508

Output random number

| 31                | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20   | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|----|----|----|----|----|----|----|----|-----|-----|------|-----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                   |    |    |    |    |    |    |    |    |     |     |      |     |    |    |    |    |    |    |    |    |    |   |   | А | А | А | А | А | А | А | А |

| 0                 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Value Description |    |    |    |    |    |    |    |    |     |     |      |     |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| [0255]            |    |    |    |    |    |    |    |    | ner | ate | d ra | and | om | nu | mb | er |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

uint8\_t nrf\_rng\_random\_value\_get(void) {

return (uint8\_t)(NRF\_RNG->VALUE & RNG\_VALUE\_VALUE\_Msk);

Remember: at the very bottom these are still just memory reads and writes!

uint32\_t value = NRF\_RNG->Value;

Is equivalent to

uint32\_t value = \*(uint32\_t\*)(0x4000D508);

### LED Blinking Code Example

## LAB HARDWARE

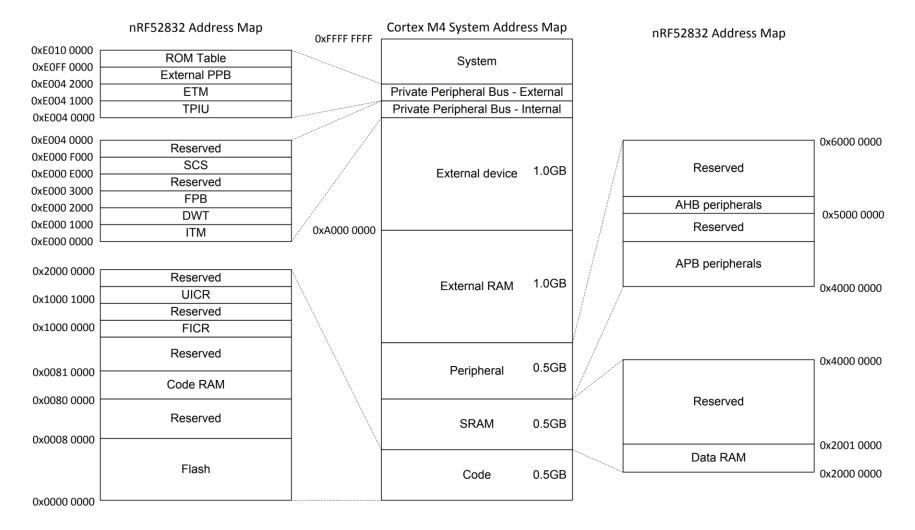

### nRF52832 Microcontroller

### Processor

- ARM Cortex-M4F

- 3-stage pipeline!

- Floating point support

### Memory

- Instruction Cache

- Off by default

- 64 kB SRAM

- 512 kB Flash

### Memory Map

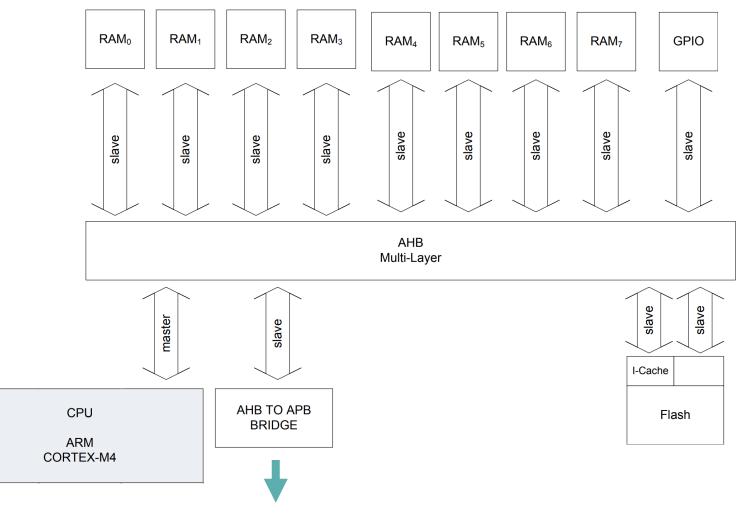

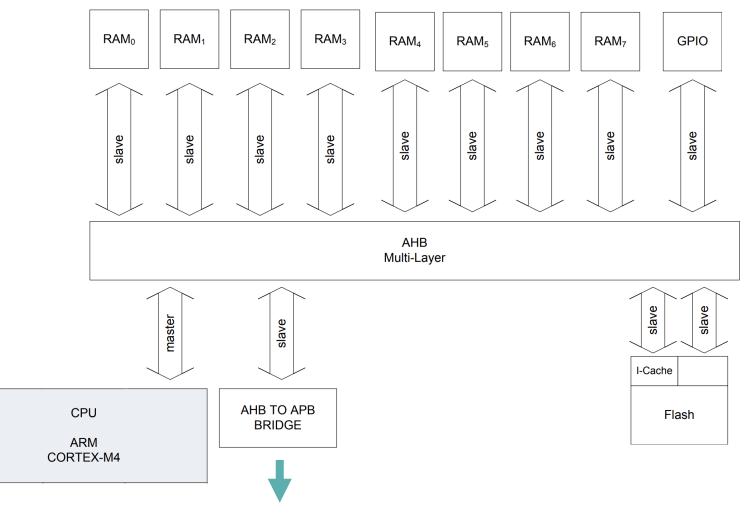

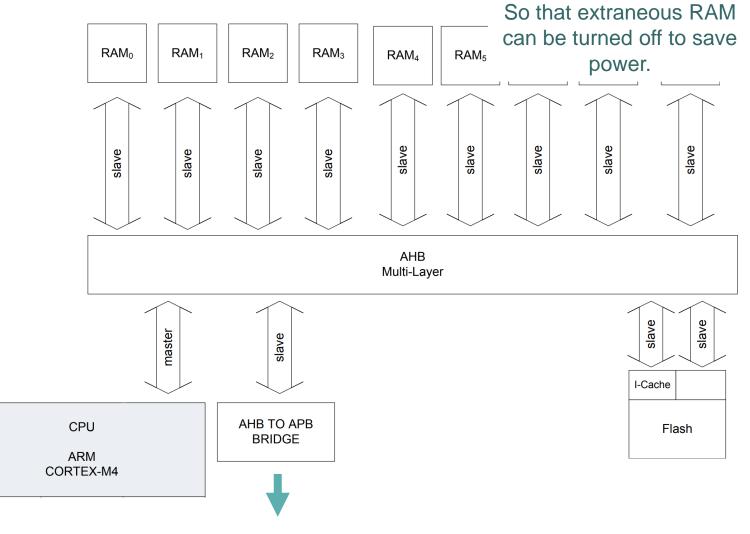

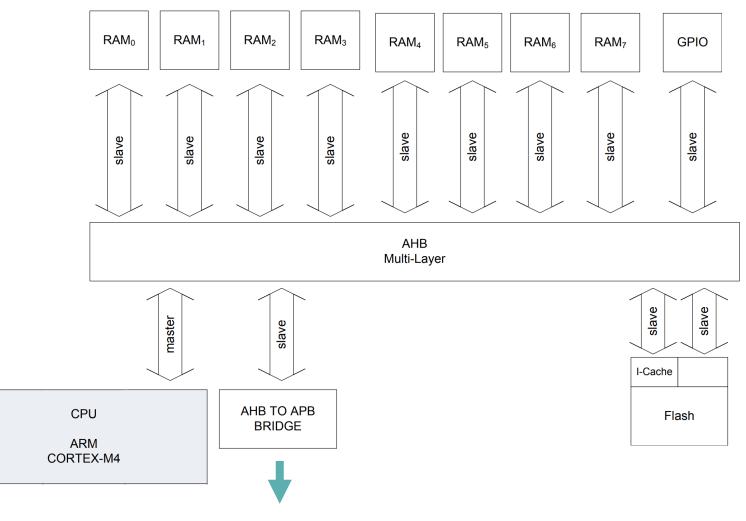

### nRF52832 Block Diagram

To Peripherals

### nRF52832 Block Diagram

## Why have 8 separate RAM banks?

To Peripherals

### nRF52832 Block Diagram

## Why have 8 separate RAM banks?

To Peripherals

### nRF52832 Block Diagram Why is GPIO special?

To Peripherals

### nRF52832 Block Diagram Why is GPIO special?

To Peripherals

### **Announcements Placeholder**

### Outline

### o Memory Overview

- Types of Memory

- Memory Hierarchy

### o Embedded Systems Memory

- Memory Maps

- Memory-Mapped I/O

- Lab Hardware Examples

### o Memory Organization

- Stacks & Heaps

- Code examples

## MEMORY LAYOUT

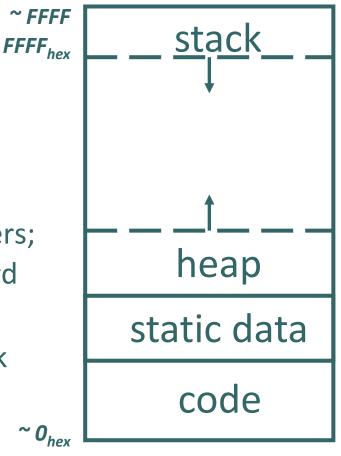

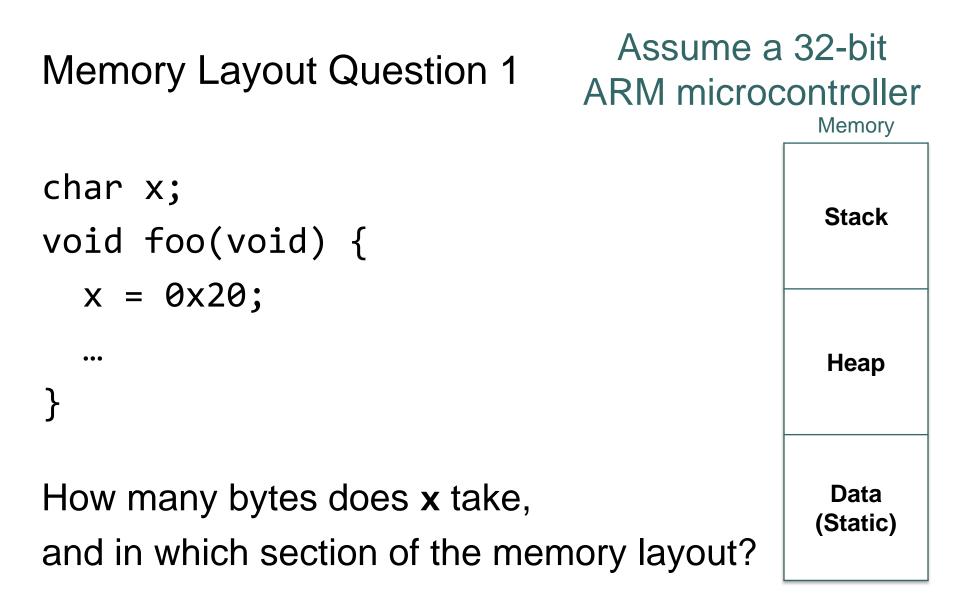

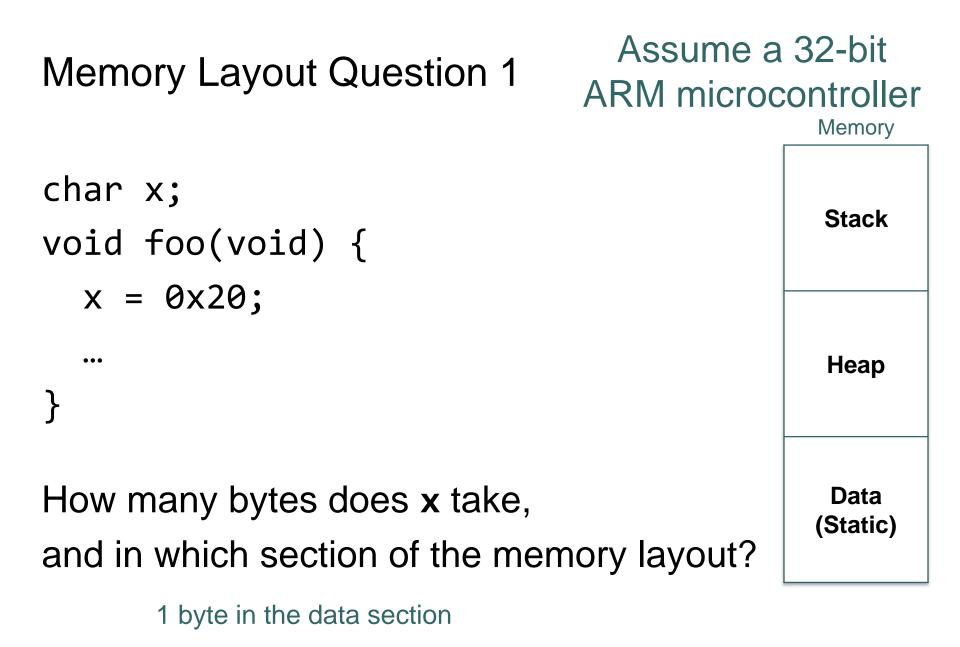

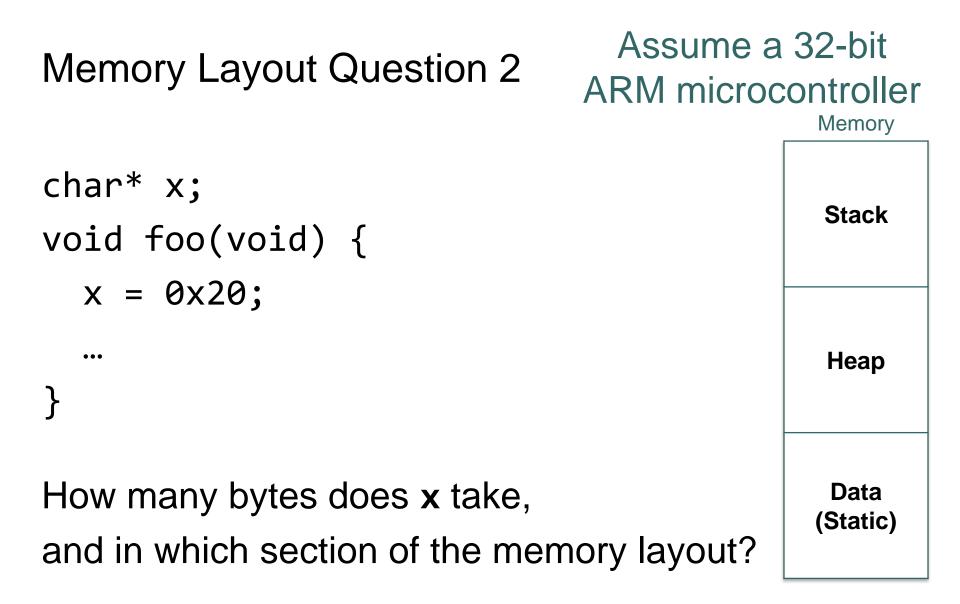

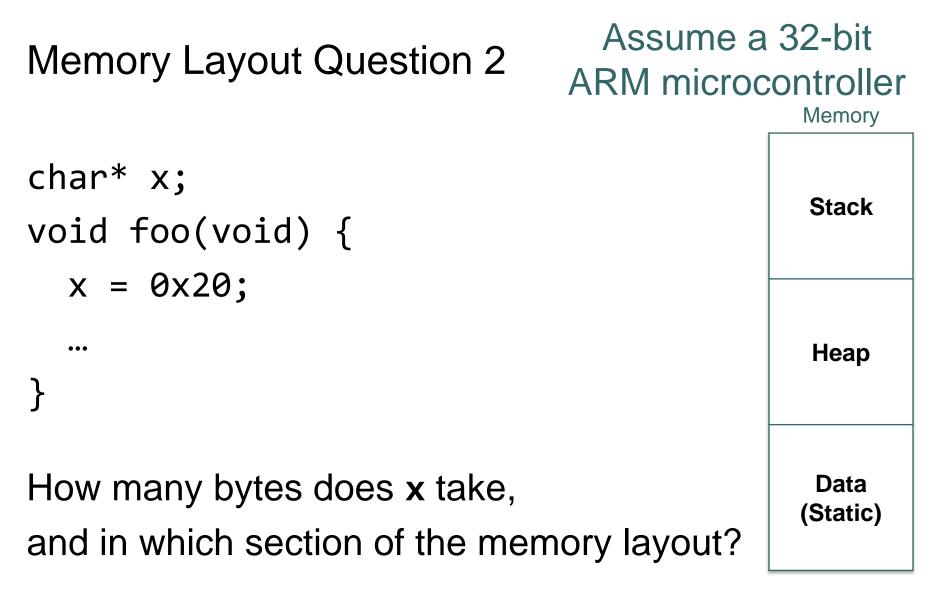

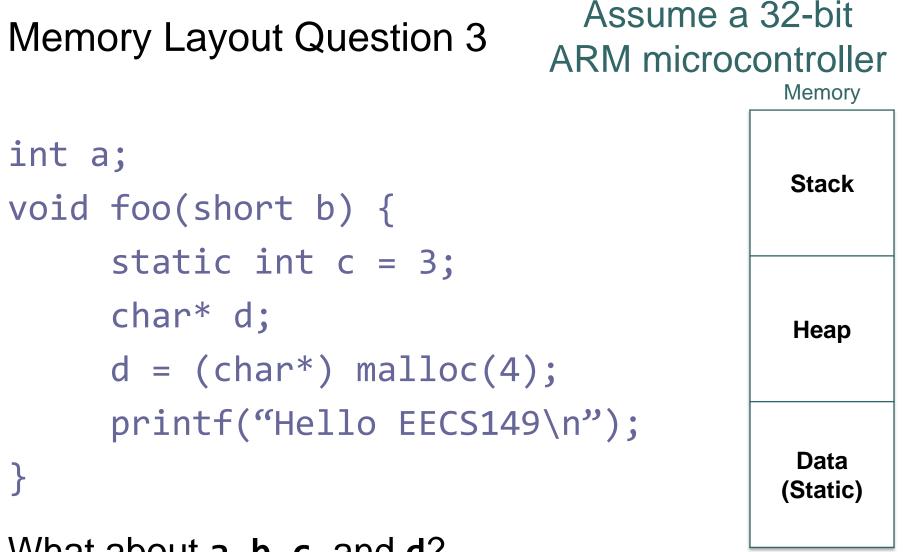

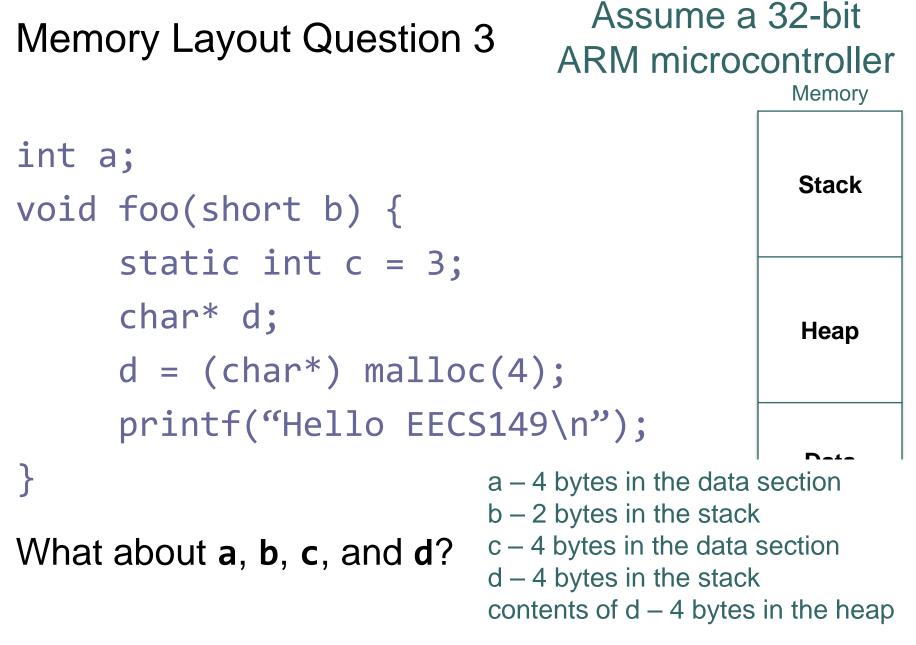

## C Memory Layout

- Program's address space contains 4 regions:

- Stack: local variables, grows downward

- Heap: space requested via malloc() and used with pointers; resizes dynamically, grows upward

- Static Data: global and static variables, does not grow or shrink

- Code: loaded when program starts, does not change

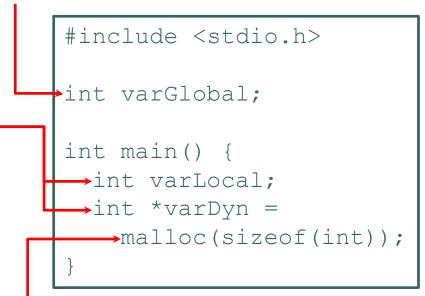

## Where Do the Variables Go?

- Declared outside a function: Static Data

- Declared inside a function:

Stack

- main() is a function

- Freed when function returns

- Dynamically allocated:

- Неар

- i.e. malloc

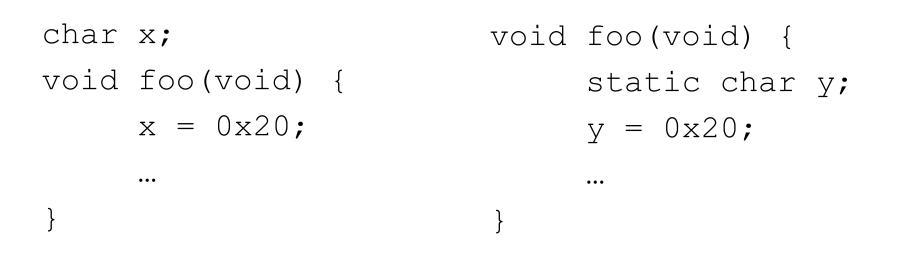

### Statically-Allocated Memory in C

Compiler chooses what address to use for x, and the variable is accessible across procedures. The variable's lifetime is the total duration of the program execution.

### Statically-Allocated Memory with Limited Scope

```

void foo(void) {

static char y;

y = 0x20;

...

}

```

Compiler chooses what address to use for y, but the variable is meant to be accessible only in foo(). The variable's lifetime is the total duration of the program execution (values persist across calls to foo()).

### Statically-Allocated Memory with Limited Scope

What is the difference between x and y when code is loaded on the device?

### Statically-Allocated Memory with Limited Scope

What is the difference between x and y when code is loaded on the device? There is no difference! Accessibility of a variable is a compile-time concept, not a run-time one.

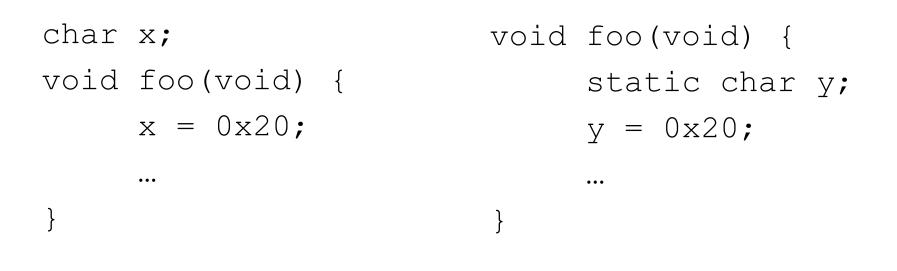

```

Variables on the Stack ("automatic variables")

```

```

void foo(void) {

char x;

x = 0x20;

...

}

```

When the procedure is called, x is assigned an address on the stack (by decrementing the stack pointer). When the procedure returns, the memory is freed (by incrementing the stack pointer). The variable persists only for the duration of the call to foo().

4 bytes in the data section (for 32-bit processors)

### What about **a**, **b**, **c**, and **d**?

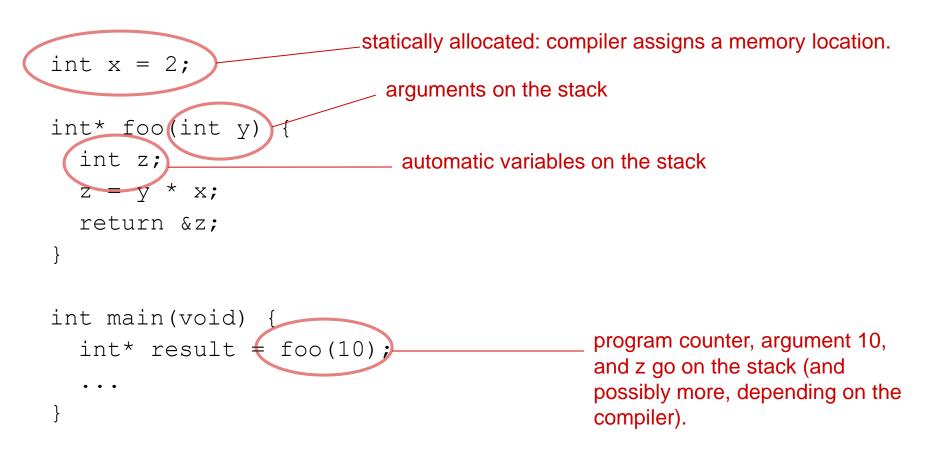

### Find the flaw in this program

(begin by thinking about where each variable is allocated)

```

int x = 2;

int* foo(int y) {

int z;

z = y \star x;

return &z;

}

int main(void) {

int^* result = foo(10);

. . .

}

```

### Solution: Find the flaw in this program

The procedure foo() returns a pointer to a variable on the stack. What if another procedure call (or interrupt) occurs before the returned pointer is de-referenced?

### The embedded systems perspective

The embedded systems perspective

# The Heap is EVIL!!!!

Why?

### Dynamically-Allocated Memory The Heap

An operating system typically offers a way to dynamically allocate memory on a "heap".

Memory management (malloc() and free()) can lead to many problems with embedded systems:

- Memory leaks (allocated memory is never freed)

- Memory fragmentation (allocatable pieces get smaller)

Automatic techniques ("garbage collection") often require stopping everything and reorganizing the allocated memory. This is deadly for real-time programs. The embedded systems perspective

How do we handle memory faults?

What if the stack grows too much?

The embedded systems perspective

How do we handle memory faults?

What if the stack grows too much?

### Nothing stops it!

Hopefully the failure is easy to understand...

### Conclusion

Memories (non-volatile and volatile) are essential to computers

Embedded systems use a simplified memory architecture with only registers, SRAM, and Flash (no caches)

Memory-Mapped I/O allows interactions with embedded peripherals to look like normal memory accesses

Software creates Stack, Heap, Static, and Code sections in memory

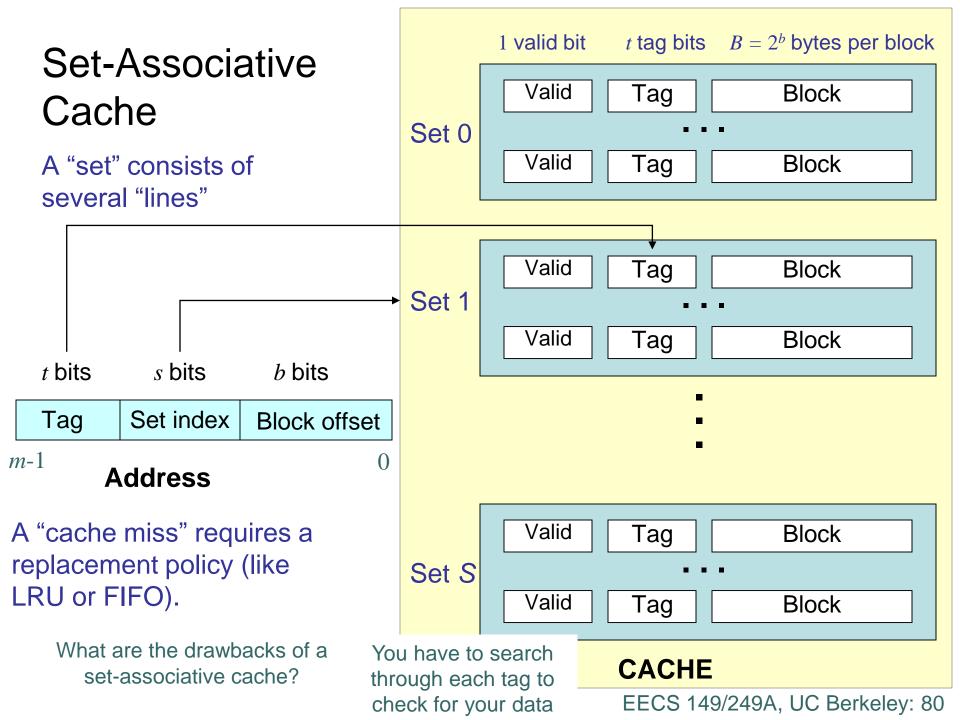

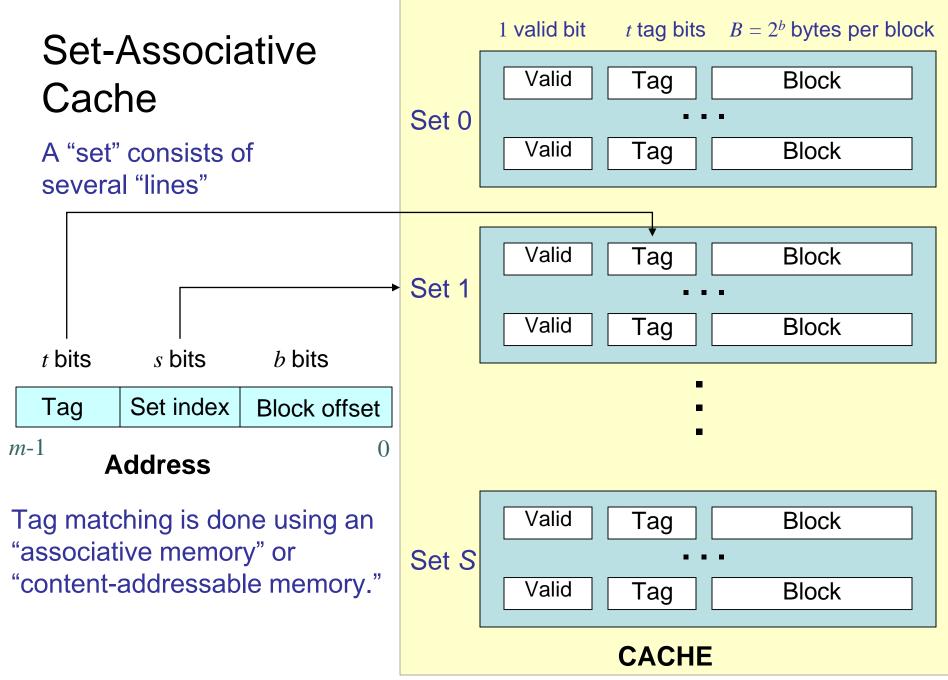

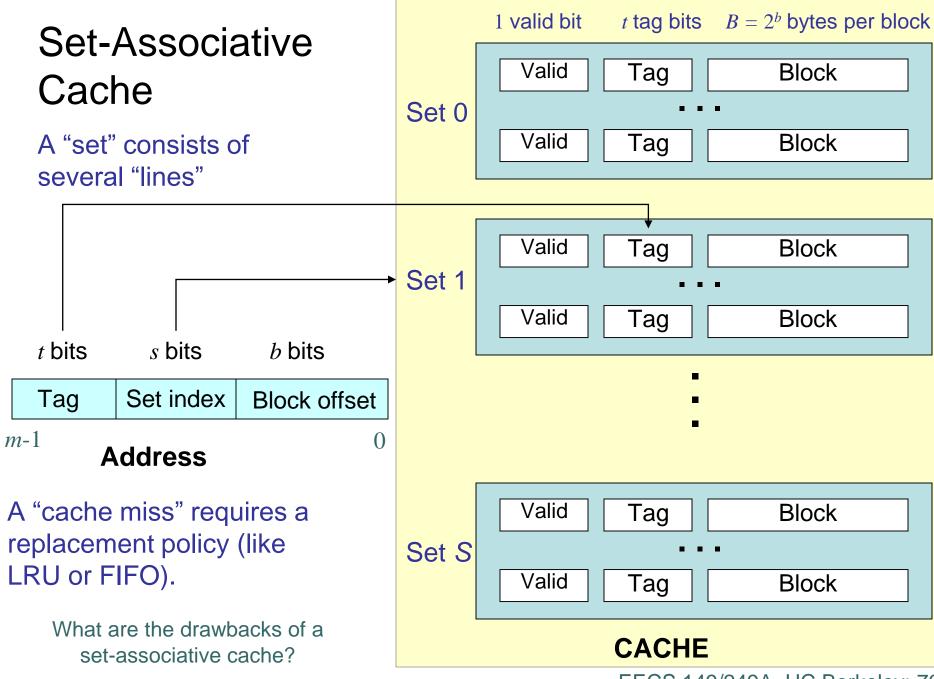

## **BONUS SLIDES ON CACHES**

See CS61C Lectures on Caches for more information <a href="https://inst.eecs.berkeley.edu/~cs61c/su19/#lectures">https://inst.eecs.berkeley.edu/~cs61c/su19/#lectures</a>

### Caches

• How do we read or write to a cache?

### Caches

#### • How do we read or write to a cache?

• You don't! Caches are automatic.

**Personal Computer**

EECS 149/249A, UC Berkeley: 77

EECS 149/249A, UC Berkeley: 78

EECS 149/249A, UC Berkeley: 79